#### ECTC 2023 Special Session 4

# Advanced Packaging Manufacturing in North America: Building the Ecosystem

Tuesday, May 30, 2023, 3:30 p.m. – 5:00 p.m.

Chairs: Nancy Stoffel (GE Research), Jan Vardaman (TechSearch International), and William Chen (ASE)

#### ECTC 2023 Special Session 4

Chair Nancy Stoffel **GE Research**

Chair William Chen **ASE**

Chair Jan Vardaman TechSearch International

**Panelist** Frank Gayle NIST

**Panelist Carl McCants** DARPA

Joshua Dillon Marvell Technology Inc.

**Panelist** Subramanian Iyer UCLA

**Panelist** Dick Otte Promex Industrics, Inc.

**Panelist** Hem P. Takiar Micron Technology Inc.

#### Advanced Packaging Manufacturing in North America: Building the Ecosystem

North America has companies that excel in design for electronics systems, device, and advanced packaging. However less than 2% of the packaging occurs in the US. This session will discuss the ambitious goals being set through the CHIPS ACT to bring Advanced Packaging to North America. We will review the targets and developing plans of the US government, funded through the CHIPS Act. The panelists will overview major initiatives launched in R&D and Manufacturing. We will also discuss the challenges to meeting the goals.

## Manufacturing 3-Dimensional Heterogeneously Integrated (3DHI) Microsystems

Dr. Carl McCants, DARPA Special Assistant - ERI

Briefing Prepared for 2023 IEEE Electronic Components and Technology Conference

May 30, 2023

#### DISRUPTIVE MICROSYSTEMS

Gaining an advantage in sensing the physical world

Securing communications

Increasing the effectiveness of radiation on target

Embedding accurate positioning and timing

#### EDGE PROCESSING

Increasing information processing efficiency at the edge

Accelerating innovation in AI hardware

#### MICROSYSTEMS MANUFACTURE

Manufacturing complex 3D microsystems

Optimizing design and test for complex circuits

Overcoming security threats across the entire hardware lifecycle

Developing electronics for extreme environments

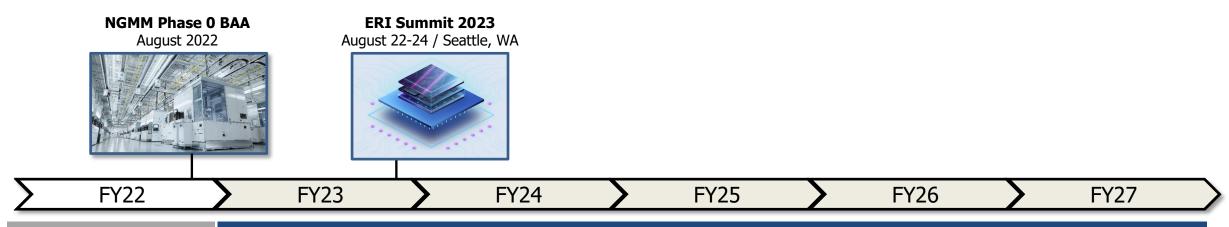

#### Electronics Resurgence Initiative (ERI) 2.0 timeline

**Original ERI**

ERI 2.0: Reinventing microsystems manufacturing for a new age

Securing communications

COMPUTE

Increasing information processing efficiency at the edge

Accelerating innovation in AI hardware

Manufacturing complex 3D microsystems

Optimizing design and test for complex circuits

Overcoming security threats across the entire hardware lifecycle

Developing electronics for extreme environments

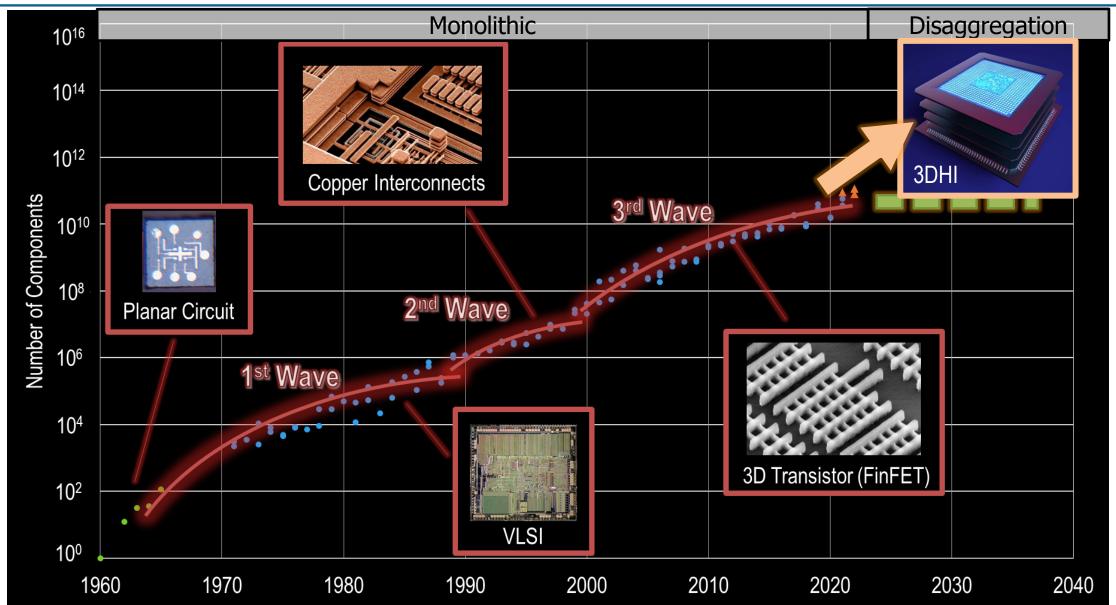

#### Disaggregation\*

Source: Electronics, Volume 38, Number 8, April 19, 1965

"It may prove more economical to **build large systems out of smaller functions, which are separately packaged and interconnected**. The availability of large functions, combined with functional design and construction, should allow the manufacturer of large systems to design and construct a considerable variety of equipment both rapidly and economically."

Gordon Moore

#### \*a.k.a.

- Polylithic

- Pseudo-lithic

- Chiplet-based

- 3DHI

#### Progress in microelectronics

#### Microsystems

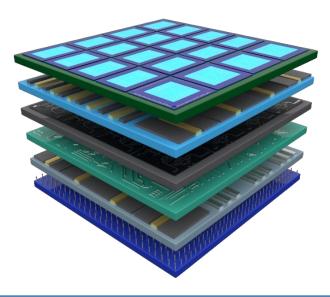

| Today                      | Future                         |

|----------------------------|--------------------------------|

| 2D                         | 3D with dense interconnects    |

| Monolithic integration     | Disaggregation                 |

| Silicon                    | Multi-process / multi-material |

| Packaged after fabrication | Packaging no longer distinct   |

#### NGMM: national capability for 3DHI R&D and low-volume manufacturing

**Users**

#### **National capability**

**Output**

Source: Adobe Stoc

Manufacturing process

3DHI assembly design kit

3DHI microsystem prototypes

#### Making 3DHI real – R&D focus areas

#### **Necessary 3DHI focus areas**

- Multi-chip, multi-technology assembly / packaging

- Compatible die-to-die, wafer-to-wafer, die-to-wafer, and wafer-to-board processes

- Desktop assembly

- 3DHI interconnects

- Precisely aligned lateral interconnects through fine-scale printing and additive manufacture

- Post-commercial-3DHI TSVs (through-substrate-via)

- Thermal and power

- Embedded thermal management within assembly and package

- Materials to extend temperature operation range

- Low-loss passives for power distribution

- Efficient power conversion in assembly / package

- Tools for design, simulation, and test

- 3DHI metrology

- Multi-domain, integrated EDA tools for 3DHI

- Validation of complete digital models

- "MOSIS-like" 3DHI prototyping services

- Baseline 3DHI fabrication processes

- 3DHI multi-project and taxi run demos with 3D-ADK (3D Assembly Design Kit)

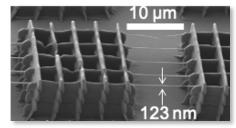

3D Microelectronics: 3D Self-Assembled Microelectronic Devices: Concepts, Materials, Applications (Adv. Mater. 15/2020)

Saha et al., Science, Vol. 366, Issue 6461, pp. 105-109, 2019

Source: Gorodenkoff

#### Making 3DHI electronics a reality requires focused R&D and pilot-line manufacturing capability

www.darpa.mil

# **ECTC Panel "CHIPS ACT Implications"**

Richard F. Otte

Promex Industries Inc.

May 30, 2023

## Where do firms, like us, find the other 2/3 of the \$?

#### "Other" Funding Sources

- Operating Funds

- Loans against Company Assets

- Industrial Partners

- Local Government. Especially States

- Professional Investors

- Family Offices

- Some Private Equity

# Who will the customers be for US based Packaging services?

- More Than Moore Concept

- Smaller nodes

- Added functionality

- Smaller Nodes Need Advanced Packaging

- Highest density devices to maximize performance

- Chiplets

- Silicon Interposers 2 micron lines & spaces

- Added Functionality Needs mostly Mainstream Packaging

- Heterogeneous Integration

- · More than Silicon on wafer

- Unique, non-electronic parts

- Standard Packages

- BGA, QFN, etc

### What Can be Done to Bring Packaging On-Shore?

- The Barriers:

- Limited on-shore capability

- Higher on-shore volume Costs

- The Benefits:

- Turn time

- Able to Visit, Communication, learn

- Alternate Source

- Confidentiality

- Consider On-Shore Carefully

#### **Overcoming On-shore Assembly Barriers**

- Focus Investment on the Emerging and Next Generations of Packaging

- Establish and Demonstrate on shore capability

- Develop Better Technologies

- Build Pilot Lines

- Demonstrate Capability & Performance

- Then Establish Relationships and then Price

- Where is the need & demand?

- Heterogeneous Integration

- Advanced Packages

- Chiplet Package Assembly